Intels Simics simulator är en helsystemsimulator som används av Intel och andra företag för att korta ner utvecklingstider och tidigarelägga utveckling av mjukvara till nya generationer av hårdvara.

Intels Simics simulator är en helsystemsimulator som används av Intel och andra företag för att korta ner utvecklingstider och tidigarelägga utveckling av mjukvara till nya generationer av hårdvara.

Ladda ner artikeln här (länk, pdf). Fler tekniska rapporter finns på etn.se/expert |

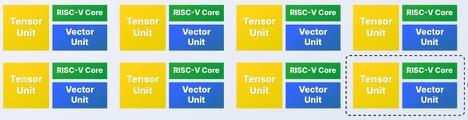

Simulatorn är också tillgänglig i en publik version för akademiker och allmänhet. Vi lade nyligen in stöd för RISC-V-arkitekturen. RISC-V ger oss en enkel arkitektur i ett enkelt system, vilket öppnar upp en del nygamla användningsfall för Intel Simics-simulatorn.

Systemmodellen

RISC-V-systemet i den publika simulatorn är en rent virtuell modell som inte motsvarar någon specifik hårdvara. Figur 1 visar systemets innehåll, vilket är tillräckligt för att boota en Linux med ett obegränsat filsystem och koppla upp systemet till lokala nätverk och Internet. Liksom alla andra Intel Simics modeller är detta en snabb funktionell modell som inte modellerar hårdvaruprestanda i någon större utsträckning.

Som Figur 1 indikerar kan man simulera flera maskiner i samma simulatorprocess, både flera kopior av RISC-V-systemet och andra system. Ett exempel på det visas i Figur 2: här simuleras en standard-PC tillsammans med ett RISC-V-system. En ssh-klient på PCn kopplar upp sig till RISC-V-systemet över nätverket inne i simulatorn. Hela nätverket kontrolleras som en enhet, och kan också kopplas upp till det externa labbnätverket eller Internet.

En kul sak som vi lärde oss när vi satte igång nätverket på RISC-V-modellen var att secure shell (SSH) kräver en viss mängd slumpdata för att fungera. Eftersom modellen är väldigt enkel så producerar Linuxen väldigt lite slump av sig själv, och det tog väldigt lång tid. Lösningen var att lägga in en simulerad hårdvaruslumpgenerator (entropy) i modellen, som snabbt (i virtuell tid) producerade de slumpdata som krävdes. Eftersom det är en simulering är de data som produceras reproducerbara, men det ser ut som bra slump från Linux perspektiv.

Lågnivåkodning

RISC-V-modellen måste inte köra Linux. RISC-V är en enkel och trevlig arkitektur som är lätt att köra ”på metallen”. Simulatorn kan ladda vanliga elf-filer som är statiskt länkade direkt till minnet. Exemplet i Figur 3 visar en liten textbaserad applikation som kör direkt på hårdvaran, utan ett operativsystem.

Ett problem med den här typen av interaktiva realtidsapplikationer är att simulatorn oftast går för fort när man kör enkel kod som det här. Simulatorns ”realtidsläge” ser till att den virtuella tiden inte går fortare än verklig tid och gör att det faktiskt går att spela ”snake” på simulerad RISC-V.

När programmet ska prata direkt med hårdvaruenheter gäller det att veta var i minnet de finns och av vilken typ de är. Figur 4 visar minnesmappen för systemet. Figur 5 visar programmeringsregistren för serieporten.

Konfiguration

RISC-V-arkitekturen är väldigt flexibel, och en viss kärna kan välja att implementera endast vissa valda grupper av instruktioner eller ’extensions’. Vår modell av RISC-V är konfigurerbar så att extensions kan slås av eller på för att bättre likna den kärna man vill simulera. Till exempel slår man av flyttalsstödet med en kodsnutt som i figur 6.

Som alla andra Simics-modeller kan man också konfigurera och bygga om hårdvaran. Aspekter som antalet kärnor och storleken på minnet och diskar ändras med enkla parametrar till systemet. För mer djupgående ändringar kan användare bygga egna hårdvarumodeller (till exempel med Intels Device Modeling Language, se Elektroniktidningen NNN) och lägga till i minnesmappen.

Eftersom RISC-V-arkitekturen är öppen kommer det hela nya förslag på utökningar och nya versioner av befintliga instruktioner. Detta gör att modellen aldrig blir ”klar”. Precis vilka utökningar som implementeras i modellen beror på precis vilka tillämpningar som RISC-V-modellen får.